4月19日-21日,第83屆中國教育裝備展示會在重慶舉辦。作為核心計算設備及算法提供者,奕斯偉計算“教育小腦”邊緣智能站助力智慧實驗廠商展示了基于AI技術的智慧實驗考試、教學場景解決方案。

智慧教育解決方案展示現(xiàn)場

奕斯偉計算“教育小腦”邊緣智能站是以邊緣計算+AI技術為核心打造的聚集高效率、高性價比的理化生實驗教學和考試等場景的智能化方案,助力教育設備客戶實現(xiàn)數(shù)字化、智能化升級。

奕斯偉計算“教育小腦”邊緣智能站

以教育小腦為核心的理化生智能實驗方案特點:

邊緣計算、實時分析:依托邊緣算力,基于需求靈活配置,實現(xiàn)高效實時分析;

通用化設計、跨平臺開發(fā):標準Restful接口設計,可輸出多模態(tài)算法結果,支持各類實驗應用的跨平臺開發(fā);

快速開發(fā)、快速迭代:內(nèi)置基礎開發(fā)框架,簡化開發(fā)流程、縮短開發(fā)周期、標準化開發(fā)提升代碼質(zhì)量;

云邊協(xié)同、遠程運維:遠程設備管理、OTA升級,有效降低運維成本。

貼近科學 覆蓋全面

教育小腦緊貼學科需求,在教學、練習、考試各個環(huán)節(jié)實現(xiàn)AI賦能,支持AI教學實時賦分、考試結束離線后集中評分等模式。

內(nèi)置算法目前已支持100+種實驗器材檢測,近100種實驗操作行為識別,40+完整大綱要求必做理化生實驗,能提供實時分析,可采用多模態(tài)算法識別結果,便于客戶直接對接應用。

低代碼快速開發(fā) 助力廠商高性價比、高效開發(fā)算法

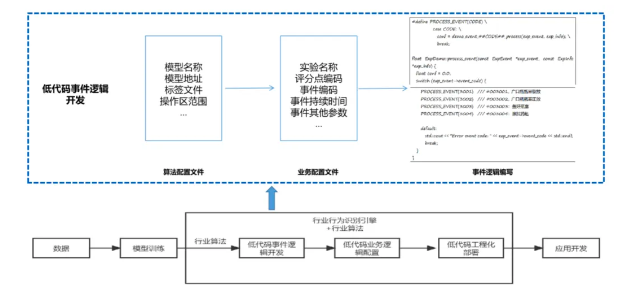

除教育小腦內(nèi)置算法外,客戶開發(fā)人員可利用內(nèi)置AI開發(fā)框架快速開發(fā)算法。內(nèi)置的AI開發(fā)框架對理化生實驗算法開發(fā)過程中涉及的推拉流、前后處理、算法平滑、對外接口等通用部分進行標準化封裝,開發(fā)人員只需關注事件邏輯本身的編碼,可大大提升開發(fā)效率和開發(fā)質(zhì)量。

奕斯偉計算“教育小腦”行業(yè)算法開發(fā)流程

RISC-V邊緣計算SoC 助力下一代教育小腦

搭載奕斯偉計算自研RISC-V邊緣計算芯片EIC7700的下一代教育小腦即將推出,以更優(yōu)性能助力客戶智能化轉型。

EIC7700在多項指標層面均實現(xiàn)了“進化”。EIC7700采用4核64位支持亂序執(zhí)行RISC-V處理器及自研高能效NPU矩陣和矢量計算模塊,支持大語言模型;DNN提供13.3TOPS INT8算力,可滿足分類、檢測、分割、追蹤相關的各類需求;具備強大視頻編解碼能力,支持32路1080P 30幀的視頻解碼能力和13路1080P 30幀的視頻編碼能力,可與推理功能并行,圖像信號處理器(ISP)可提供圖像增強、動態(tài)對比度增強、畸變校正等多種圖像處理硬件加速功能;擁有豐富的多媒體輸入輸出、PCIe、以太網(wǎng)等外部接口。

搭載EIC7700的新一代教育小腦針對教育場景下的AI應用,在計算算子、軟件工具等方面做了專門優(yōu)化,同時搭配奕斯偉計算自研AI智慧實驗框架及算法,可提供性能更優(yōu)、性價比更高的智慧教育解決方案。

2024世界數(shù)字教育大會上,中國科學院院士、教育部黨組書記及部長懷進鵬指出:智能化是教育變革的重要引擎,我們將實施人工智能賦能行動,促進智能技術與教育教學(AI for Education)、科學研究(AI for Science)、社會(AI for Society)的深度融合,為學習型社會、智能教育和數(shù)字技術發(fā)展提供有效的行動支撐。這也是奕斯偉計算“教育小腦”解決方案助力客戶要實現(xiàn)的重要目標。